# **SM7000 SERIES**

## **MICROWAVE SWITCH**

## USER'S MANUAL

82-0046-000 Release May 6, 2003

VXI Technology, Inc. 2031 Main Street Irvine, CA 92614-6509 (949) 955-1894

### TABLE OF CONTENTS

| Certification                                                         |   |

|-----------------------------------------------------------------------|---|

| Warranty                                                              |   |

| Limitation of Warranty                                                |   |

| Restricted Rights Legend                                              | 6 |

| DECLARATION OF CONFORMITY                                             |   |

| GENERAL SAFETY INSTRUCTIONS                                           |   |

| Terms and Symbols                                                     |   |

| Warnings                                                              |   |

| SUPPORT RESOURCES                                                     |   |

| SECTION 1                                                             |   |

| INTRODUCTION                                                          |   |

| Overview                                                              |   |

| SM7000 Series Switch Options                                          |   |

| Programming                                                           |   |

| Automatic Scanning                                                    |   |

| Programmable Timing Delays                                            |   |

| Safety Interrupt                                                      |   |

| Break-Before-Make / Make-Before-Break Operation                       |   |

| SM7000 Series Specifications                                          |   |

| SECTION 2                                                             |   |

| PREPARATION FOR USE                                                   |   |

| Introduction                                                          |   |

| Calculating System Power and Cooling Requirements                     |   |

| Setting the Chassis Backplane Jumpers                                 |   |

| Setting the Logical Address                                           |   |

| Selecting the Extended Memory Space                                   |   |

| SECTION 3                                                             |   |

| PROGRAMMING                                                           |   |

| Register Access                                                       |   |

| Addressing                                                            |   |

| Description of Registers - A16                                        |   |

| Description of SMIP II Module Registers - A24 / A32 - Extended Memory |   |

| DEVICE MEMORY MAP                                                     |   |

| Module Relay Control Address                                          |   |

| Relay Register Offset                                                 |   |

| Writing to the Relays                                                 |   |

| Programming                                                           |   |

| SECTION 4                                                             |   |

| SWITCH CONFIGURATION                                                  |   |

| Introduction                                                          |   |

| SM7000 CONFIGURATION                                                  |   |

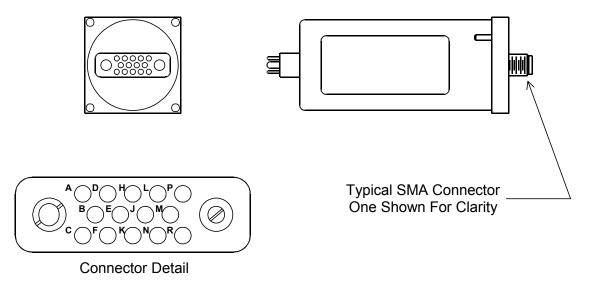

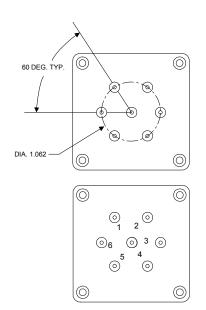

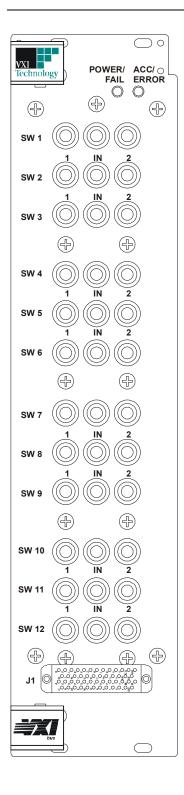

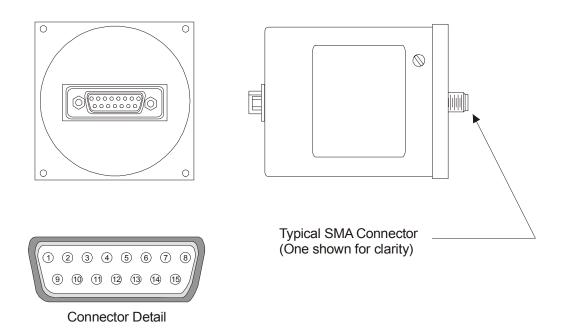

| Front Panel Connection - SM7000                                       |   |

| SM7000 Connector Pin Assignments                                      |   |

| SM7000 Relay Identification Table                                     |   |

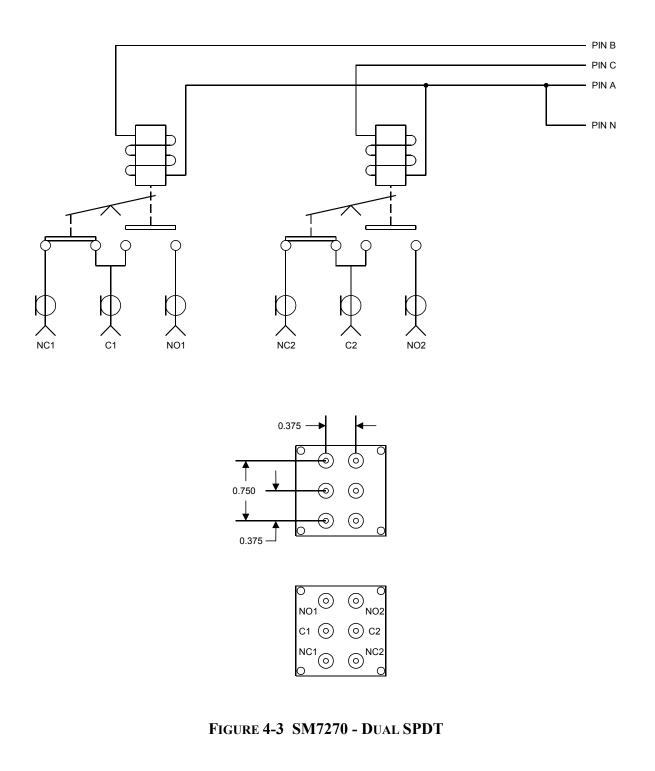

| SM7270 - Dual SPDT                                                    |   |

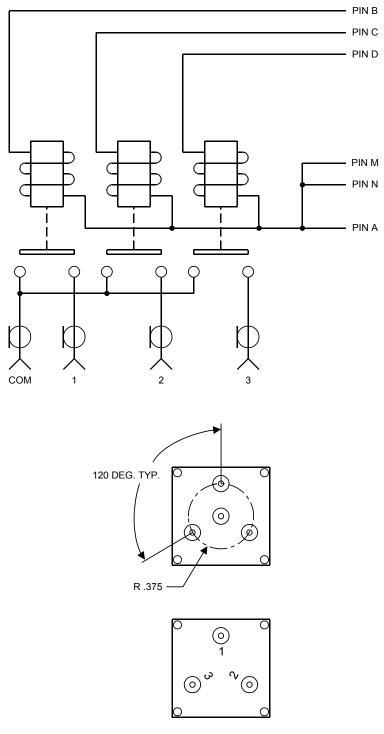

| SM7271 - SP3T                                                         |   |

| SM7272 - SP4T                                                         |   |

| SM7273 - SP5T<br>SM7274 - SP6T                                        |   |

| SM/2/4 - SP01<br>SM7275 - Transfer Switch                             |   |

|                                                                       |   |

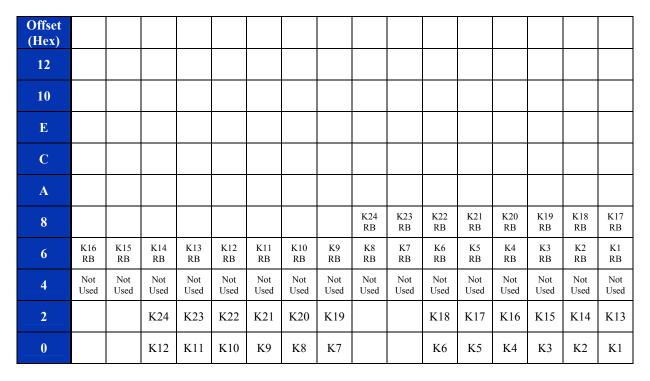

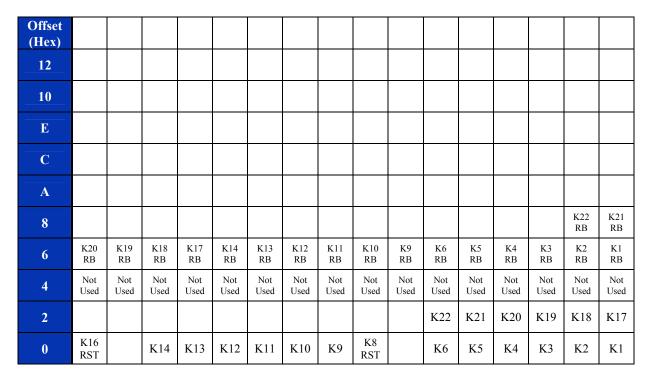

| SM7000 Microwave Switch Relay Register Map                             | 51 |

|------------------------------------------------------------------------|----|

| SM7000 Switch / Relay Chart                                            | 51 |

| SM7001A CONFIGURATION                                                  |    |

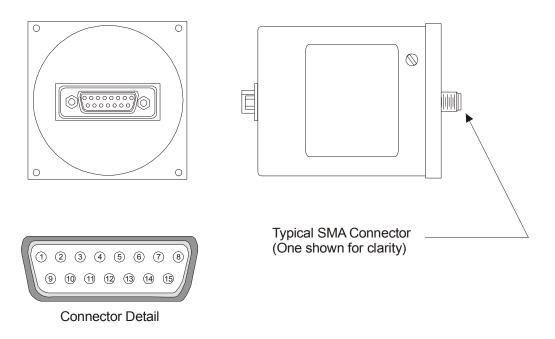

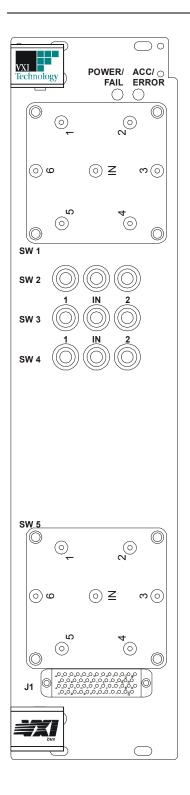

| Front Panel Connection - SM7001A                                       |    |

| SM7001A Connector Pin Assignments - Interface to SMIP II Platform      | 53 |

| Switch Option (SM73XX) to SM7001A Connection                           | 53 |

| SM7001A Relay Identification Table                                     | 54 |

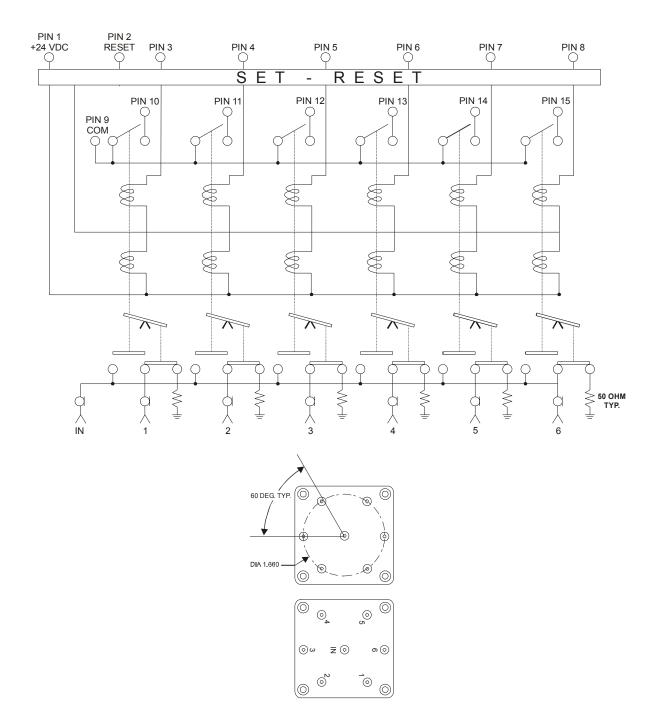

| SM7374 - SP6T                                                          |    |

| SM7001A Microwave Switch Relay Register Map                            | 55 |

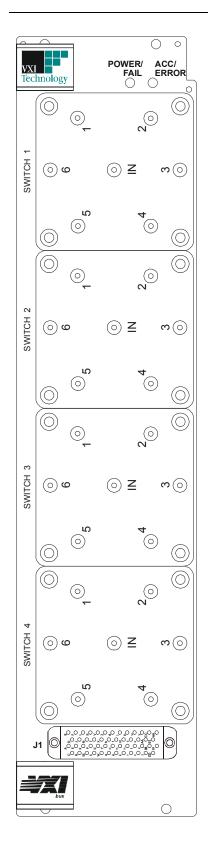

| SM7001L CONFIGURATION                                                  |    |

| Front Panel Connection - SM7001L                                       |    |

| Switch Module Installation                                             |    |

| Switch Module Operation                                                |    |

| SM7001L Connector Pin Assignments - Interface to SMIP II Platform      |    |

| Switch Option (SM7374L) to SM7001L Connection                          |    |

| SM7374L - SP6T                                                         |    |

| SM7002 CONFIGURATION                                                   |    |

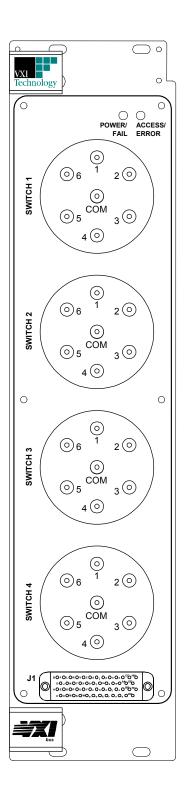

| Front Panel Connection - SM7002                                        |    |

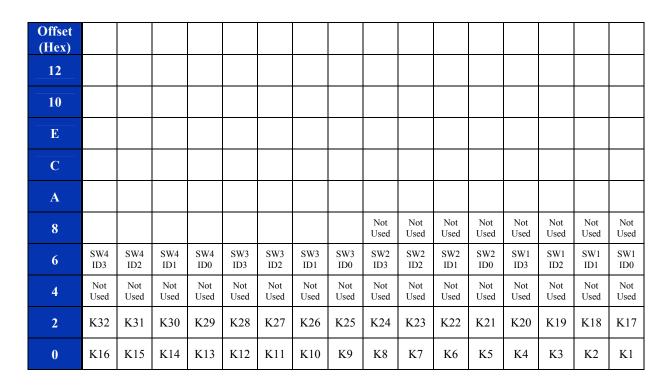

| SM7002 Microwave Switch Relay Register Map                             |    |

| SM7012L CONFIGURATION                                                  |    |

| Front Panel Connection - SM7012L                                       |    |

| Switch Module Operation                                                |    |

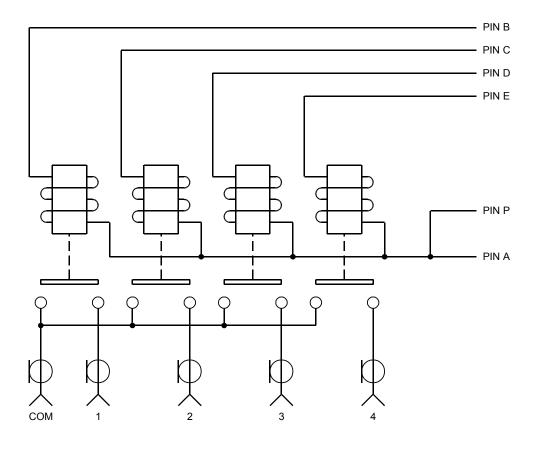

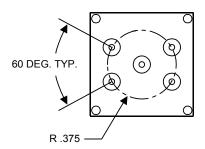

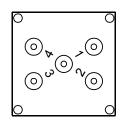

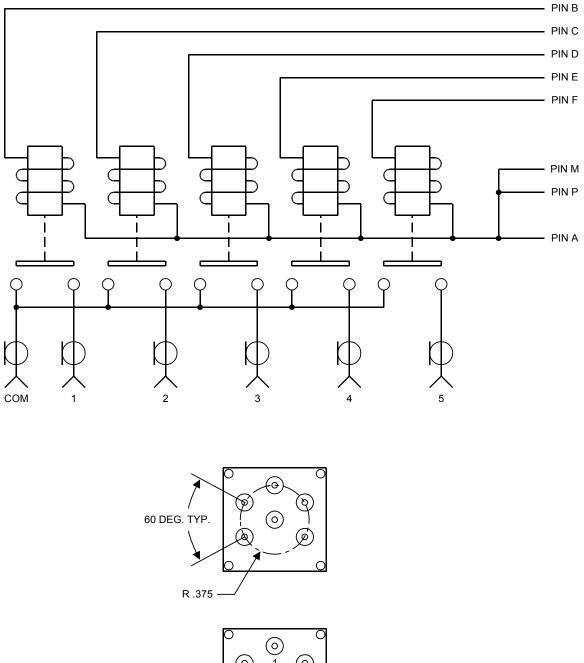

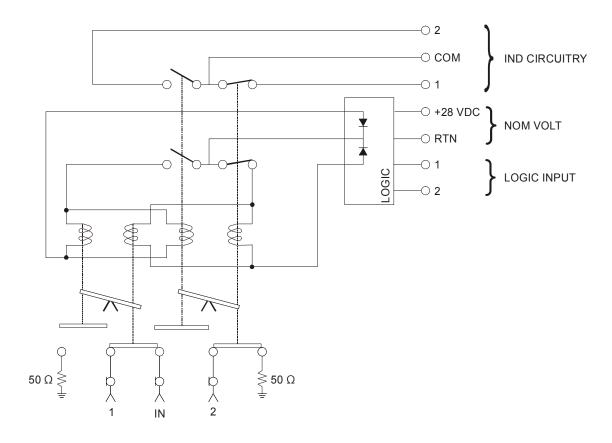

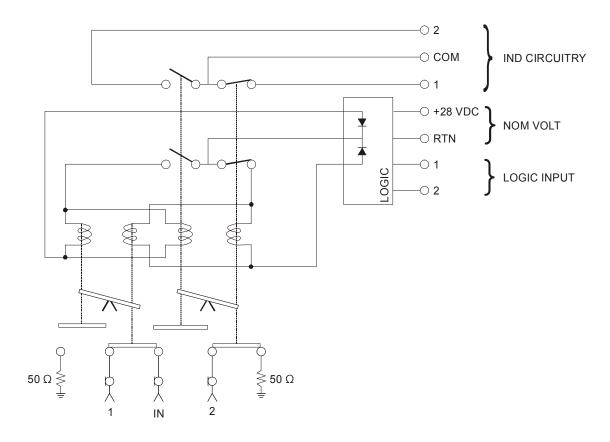

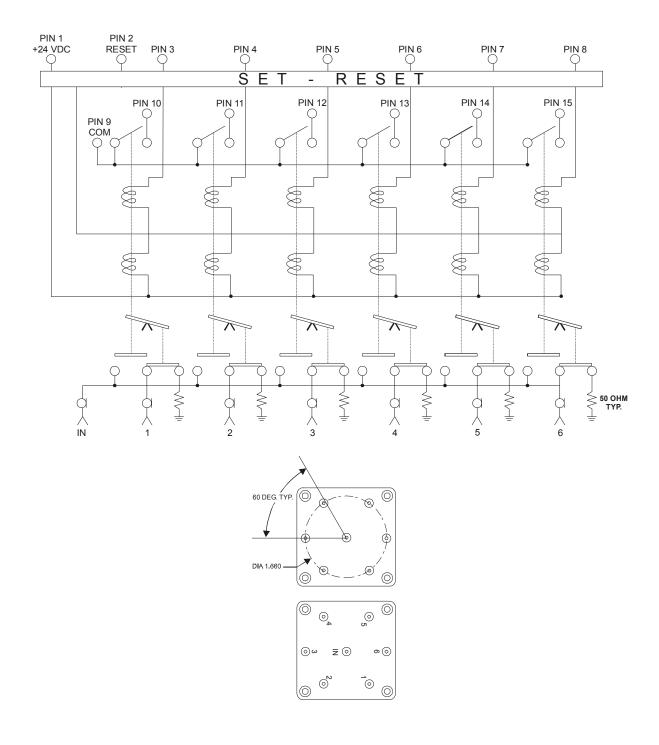

| SPDT Switch Schematic                                                  |    |

| SM7012L Microwave Switch Relay Register Map                            |    |

| SM7013L CONFIGURATION                                                  |    |

| Front Panel Connection - SM7013L                                       |    |

| Switch Module Installation                                             |    |

| Switch Module Operation                                                |    |

| Switch Option (SM7374L) to SM7013L Connection                          |    |

| SPDT Switch Schematic                                                  |    |

| SM7374L - SP6T                                                         |    |

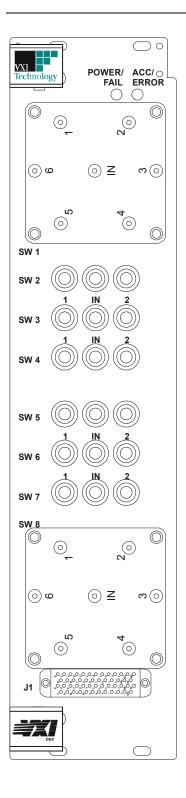

| SM7016L CONFIGURATION                                                  |    |

| Front Panel Connection - SM7016L                                       |    |

| Switch Module Installation                                             |    |

| Switch Module Operation                                                |    |

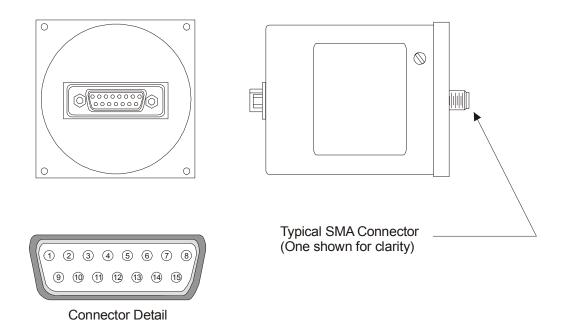

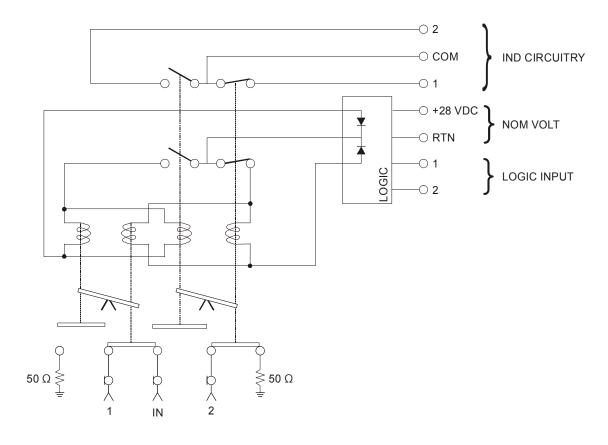

| Switch Option (SM7374L) to SM7016L Connection                          |    |

| SPDT Switch Schematic                                                  |    |

| SM7374L - SP6T                                                         |    |

| 32 CHANNEL RELAY DRIVER                                                |    |

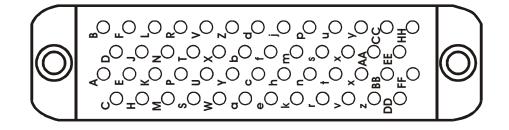

| Pin Assignments - J1                                                   |    |

| 50-Pin Connector Detail                                                |    |

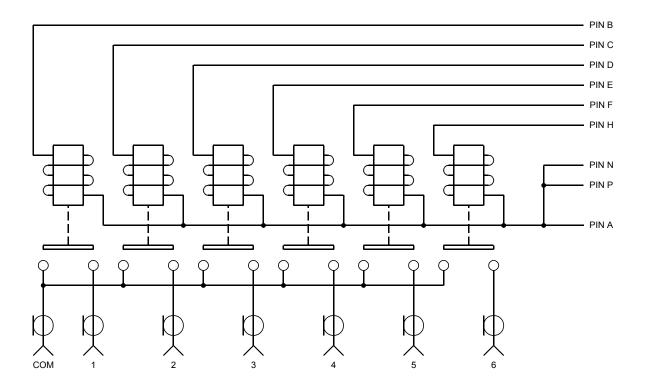

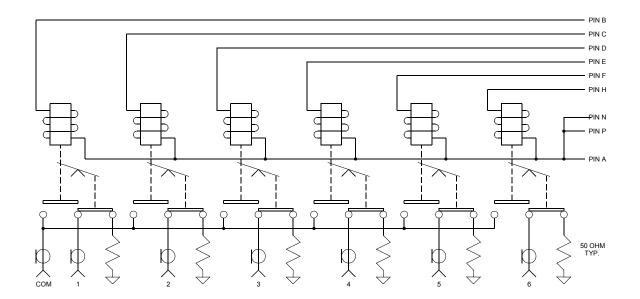

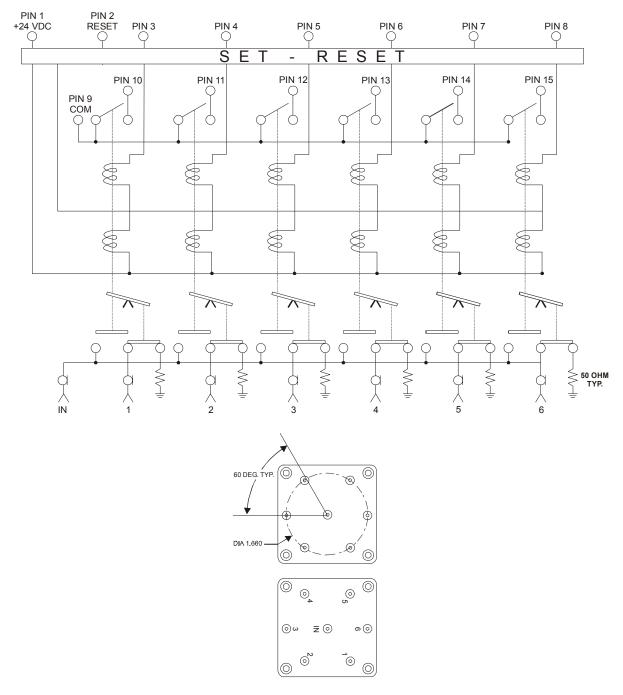

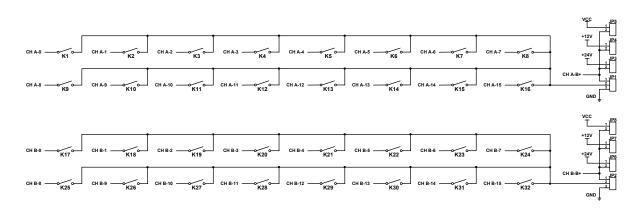

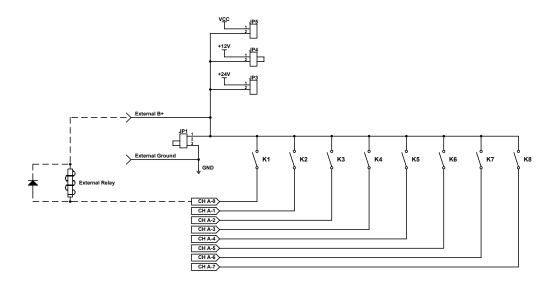

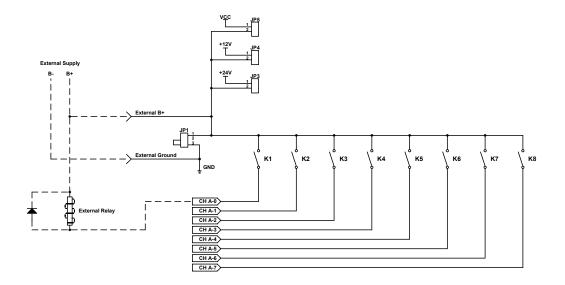

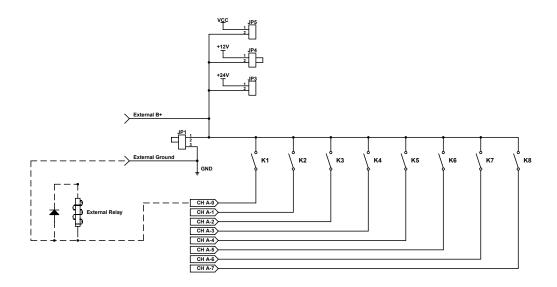

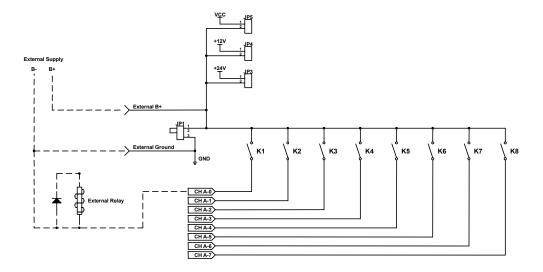

| 32 Channel Relay Driver Schematic                                      |    |

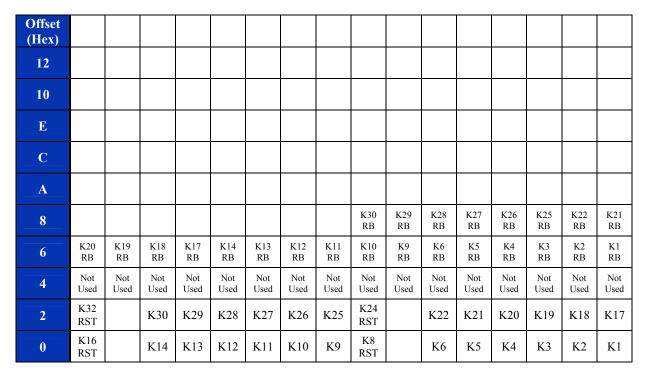

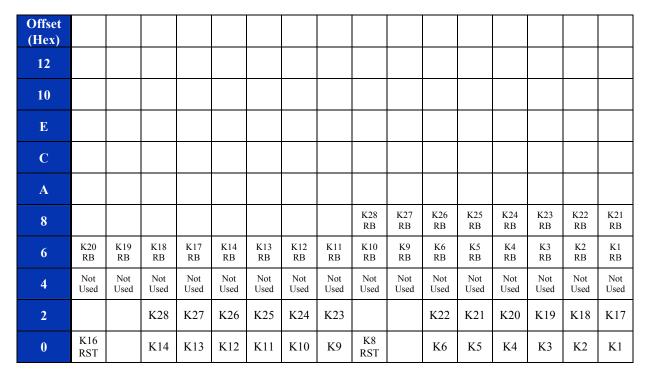

| Relay Driver Register Map                                              |    |

| Interface Examples                                                     |    |

| PASS-THROUGH ADAPTERS                                                  |    |

| Introduction                                                           |    |

| Table 4-25 SM7000/7001A Pass-Through Adapter Connector Pin Assignments |    |

| Pass-Through Adapters - Connection Examples                            |    |

|                                                                        |    |

| DEX                                                                    |    |

www.vxitech.com

#### CERTIFICATION

VXI Technology, Inc. (VTI) certifies that this product met its published specifications at the time of shipment from the factory. VTI further certifies that its calibration measurements are traceable to the United States National Institute of Standards and Technology (formerly National Bureau of Standards), to the extent allowed by that organization's calibration facility, and to the calibration facilities of other International Standards Organization members.

#### WARRANTY

The product module (SM7000/7001A/7001L/7012L) referred to herein is warranted against defects in material and workmanship for a period of three years from the receipt date of the product at customer's facility. The same warranty applies to the product options (SM72XX/73XX/73XXL) and the SM7002 for a period of one year. The sole and exclusive remedy for breach of any warranty concerning these goods shall be repair or replacement of defective parts, or a refund of the purchase price, to be determined at the option of VTI.

For warranty service or repair, this product must be returned to a VXI Technology authorized service center. The product shall be shipped prepaid to VTI and VTI shall prepay all returns of the product to the buyer. However, the buyer shall pay all shipping charges, duties, and taxes for products returned to VTI from another country.

VTI warrants that its software and firmware designated by VTI for use with a product will execute its programming when properly installed on that product. VTI does not however warrant that the operation of the product, or software, or firmware will be uninterrupted or error free.

#### LIMITATION OF WARRANTY

The warranty shall not apply to defects resulting from improper or inadequate maintenance by the buyer, buyersupplied products or interfacing, unauthorized modification or misuse, operation outside the environmental specifications for the product, or improper site preparation or maintenance.

VXI Technology, Inc. shall not be liable for injury to property other than the goods themselves. Other than the limited warranty stated above, VXI Technology, Inc. makes no other warranties, express or implied, with respect to the quality of product beyond the description of the goods on the face of the contract. VTI specifically disclaims the implied warranties of merchantability and fitness for a particular purpose.

#### **RESTRICTED RIGHTS LEGEND**

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subdivision (b)(3)(ii) of the Rights in Technical Data and Computer Software clause in DFARS 252.227-7013.

VXI Technology, Inc. 2021 Main Street Irvine, CA 92614-6509 U.S.A.

#### **DECLARATION OF CONFORMITY** Declaration of Conformity According to ISO/IEC Guide 22 and EN 45014

| MANUFACTURER'S NAME    | VXI Technology, Inc.                                        |

|------------------------|-------------------------------------------------------------|

| MANUFACTURER'S ADDRESS | 2031 Main Street<br>Irvine, California 92614-6509           |

| PRODUCT NAME           | Microwave Switch Module                                     |

| Model Number(s)        | SM7000, SM7001A, SM7001L, SM7002, SM7012L, SM7013L, SM7016L |

| PRODUCT OPTIONS        | All                                                         |

| PRODUCT CONFIGURATIONS | All                                                         |

*VXI Technology, Inc. declares that the aforementioned product conforms to the requirements of the* Low Voltage Directive 73/23/EEC and the EMC Directive 89/366/EEC (inclusive 93/68/EEC) and carries the "CE" mark accordingly. The product has been designed and manufactured according to the following specifications:

SAFETY

EMC

EN61010 (2001)

EN61326 (1997 w/A1:98) Class A CISPR 22 (1997) Class A VCCI (April 2000) Class A ICES-003 Class A (ANSI C63.4 1992) AS/NZS 3548 (w/A1 & A2:97) Class A FCC Part 15 Subpart B Class A EN 61010-1:2001

The product was installed into a C-size VXI mainframe chassis and tested in a typical configuration.

I hereby declare that the aforementioned product has been designed to be in compliance with the relevant sections of the specifications listed above as well as complying with all essential requirements of the Low Voltage Directive.

May 2003

Pattor

Jerry Patton, QA Manager

### **GENERAL SAFETY INSTRUCTIONS**

Review the following safety precautions to avoid bodily injury and/or damage to the product. These precautions must be observed during all phases of operation or service of this product. Failure to comply with these precautions, or with specific warnings elsewhere in this manual, violates safety standards of design, manufacture, and intended use of the product.

Service should only be performed by qualified personnel.

#### **TERMS AND SYMBOLS**

These terms may appear in this manual:

| WARNING | Indicates that a procedure or condition may cause bodily injury or death.                         |

|---------|---------------------------------------------------------------------------------------------------|

| CAUTION | Indicates that a procedure or condition could possibly cause damage to equipment or loss of data. |

These symbols may appear on the product:

ATTENTION - Important safety instructions

Frame or chassis ground

#### WARNINGS

Follow these precautions to avoid injury or damage to the product:

| Use Proper Power Cord   | To avoid hazard, only use the power cord specified for this product.                                                                         |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Use Proper Power Source | To avoid electrical overload, electric shock, or fire hazard,<br>do not use a power source that applies other than the<br>specified voltage. |

| Use Proper Fuse         | To avoid fire hazard, only use the type and rating fuse specified for this product.                                                          |

#### WARNINGS (CONT)

| Avoid Electric Shock | To avoid electric shock or fire hazard, do not operate this product with the covers removed. Do not connect or disconnect any cable, probes, test leads, etc. while they are connected to a voltage source. Remove all power and unplug unit before performing any service. <i>Service should only be performed by qualified personnel.</i>                                                                                                                                         |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ground the Product   | This product is grounded through the grounding conductor<br>of the power cord. To avoid electric shock, the grounding<br>conductor must be connected to earth ground.                                                                                                                                                                                                                                                                                                               |

| Operating Conditions | <ul> <li>To avoid injury, electric shock or fire hazard:</li> <li>Do not operate in wet or damp conditions.</li> <li>Do not operate in an explosive atmosphere.</li> <li>Operate or store only in specified temperature range.</li> <li>Provide proper clearance for product ventilation to prevent overheating.</li> <li>DO NOT operate if you suspect there is any damage to this product. <i>Product should be inspected or serviced only by qualified personnel.</i></li> </ul> |

| Improper Use         | The operator of this instrument is advised that if the<br>equipment is used in a manner not specified in this manual,<br>the protection provided by the equipment may be impaired.<br>Conformity is checked by inspection.                                                                                                                                                                                                                                                          |

### **SUPPORT RESOURCES**

Support resources for this product are available on the Internet and at VXI Technology customer support centers.

#### VXI Technology World Headquarters

VXI Technology, Inc. 2031 Main Street Irvine, CA 92614-6509

Phone: (949) 955-1894 Fax: (949) 955-3041

#### VXI Technology Cleveland Division

VXI Technology, Inc. 7525 Granger Road, Unit 7 Valley View, OH 44125

Phone: (216) 447-8950 Fax: (216) 447-8951

#### VXI Technology Lake Stevens Instrument Division

VXI Technology, Inc. 1924 - 203 Bickford Snohomish, WA 98290

Phone: (425) 212-2285 Fax: (425) 212-2289

#### **Technical Support**

Phone: (949) 955-1894 Fax: (949) 955-3041 E-mail: support@vxitech.com

See http://www.vxitech.com for worldwide support sites.

## **SECTION 1**

## INTRODUCTION

#### **OVERVIEW**

The SM7000 Series microwave switching modules are members of the VXI Technology SMIP  $II^{\text{TM}}$  family. They offer a modular design allowing custom switching configurations to be easily assembled and modified in the field.

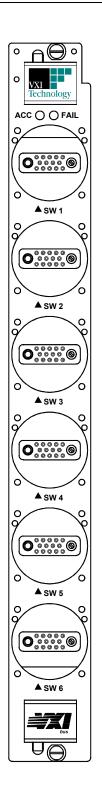

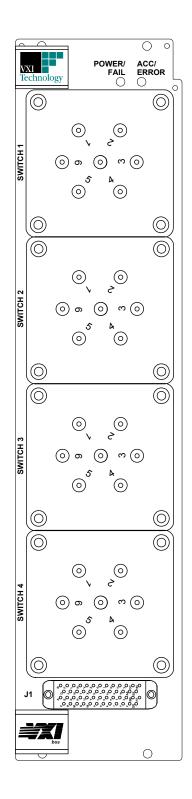

The SM7000 is a single-wide, C-size VXI module, which can support up to six different microwave switches including: a dual SPDT; SP3T through SP6T; transfer switches and pass-through adapters that allow the module to control up to eight externally mounted relays each.

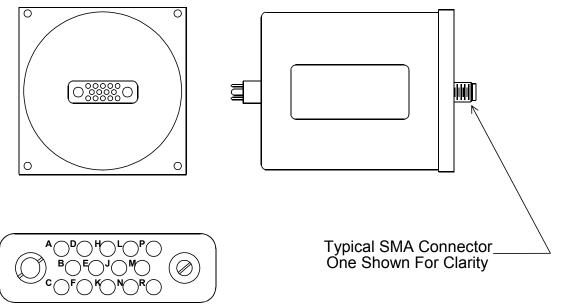

The SM7001A, SM7001L, SM7002-X and the SM7012L are double-wide, C-size VXI modules, which can support up to four different microwave switches including: a terminated SP6T and pass-though adapters that allow the module to control up to eight externally mounted relays each. The SM7001L, SM7012L, SM7013L and SM7016L differ from the other two double-wide modules in that their switches utilize latching relays.

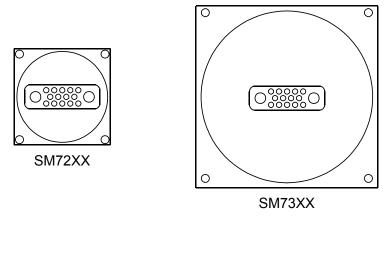

FIGURE 1-1 SM7000 (LEFT) AND SM7002 (RIGHT) MICROWAVE SWITCH MODULES

Using the SMIP *II* family for microwave switching, the user obtains the following benefits over other VXI microwave switch solutions:

| Density:    | Up to six (1 x 6) microwave relays can be housed in a single VXIbus slot (SM7000).                                                                                                                              |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Modularity: | Each SM7000 switch module can house up to six switches, or "building blocks", which can be mixed and matched for the final configuration. There are up to seven of these "building blocks" from which to chose. |

The following table lists the different switch available in the SM7000 series.

| SM7000 SERIES SWITCH OPTIONS |                           |

|------------------------------|---------------------------|

| SM7000 (DC - 18 GHz)         | Relay Type                |

| SM7270                       | Dual SPDT Fail Safe       |

| SM7271                       | SP3T Non-latching         |

| SM7272                       | SP4T Non-latching         |

| SM7273                       | SP5T Non-latching         |

| SM7274                       | SP6T Non-latching         |

| SM7275                       | Transfer Switch Fail Safe |

| SM7276                       | Pass-Through Adapter      |

| SM7001A (DC - 18 GHz)        | Relay Type                |

| SM7374                       | SP6T Non-latching         |

| SM7376                       | Pass-Through Adapter      |

| SM7000L (DC - 18 GHz)        | Relay Type                |

| SM7374L                      | SP6T Latching             |

| SM7002 (DC - 40 GHz)         | Relay Type                |

| SM7002-1                     | SP3T Non-latching         |

| SM7002-2                     | SP4T Non-latching         |

| SM7002-3                     | SP5T Non-latching         |

| SM7002-4                     | SP6T Non-latching         |

| SM7012L (DC - 18 GHz)        | Relay Type                |

| Fixed SPDT Relays            | SPDT Latching             |

| SM7013L (DC - 18 GHz)        | Relay Type                |

| <b>3</b> Fixed SPDT Relays   | SPDT Latching             |

| 2 SM7374L                    | SP6T Latching             |

| SM7016L (DC - 18 GHz)        | Relay Type                |

| 6 Fixed SPDT Relays          | SPDT Latching             |

| 2 SM7374L                    | SP6T Latching             |

#### **SM7000 SERIES SWITCH OPTIONS**

#### PROGRAMMING

The SMIP *II* family of switch modules is programmed using direct register access for fast data throughput.

#### **Automatic Scanning**

A predefined sequence of channels can be programmed into an extensive scan list that can be incremented by a trigger. This approach relieves the host controller from having to tie up the VXIbus backplane when scanning.

#### **Programmable Timing Delays**

A delay can be programmed between relay closures to allow for settling times of other system resources. When used with triggers, a controlled synchronous switching system can easily be configured.

#### **Safety Interrupt**

This is a programmable fail-safe feature that allows all relays to open based upon the occurrence of a selected TTL backplane trigger. This allows signals to be removed from the unit under test if a system fail-safe occurs, such as inadvertent removal of a test adapter.

#### Break-Before-Make / Make-Before-Break Operation

This feature allows automatic Break-Before-Make (BBM) and Make-Before-Break (MBB) operations. It is programmed simply by setting user configurable options. In BBM operation, all opening relays are guaranteed to open prior to any closing relays being set. The relay open or close time is user configurable as well. In MBB operation, the closing relays are guaranteed to be set prior to the opening relays being opened.

#### **SM7000 SERIES SPECIFICATIONS**

| SM7000 SPECIFICATIONS    |         |       |        |           |  |

|--------------------------|---------|-------|--------|-----------|--|

| MAXIMUM POWER HANDLING ( | CW)     |       |        |           |  |

| At 18 GHz                | 20 W    |       |        |           |  |

| SWITCHING TIME           |         |       |        |           |  |

|                          | < 15 ms |       |        |           |  |

| RF IMPEDANCE             |         |       |        |           |  |

|                          | 50 Ω    |       |        |           |  |

| FREQUENCY (GHz)          | DC – 3  | 3 – 8 | 8-12.4 | 12.4 - 20 |  |

| Isolation (dB min)       | 80      | 70    | 60     | 60        |  |

| Insertion Loss (dB max)  | 0.2     | 0.3   | 0.4    | 0.5       |  |

| VSWR                     | 1.2:1   | 1.3:1 | 1.4:1  | 1.5:1     |  |

| SM7001A SPECIFICATIONS   |         |       |        |           |  |

|--------------------------|---------|-------|--------|-----------|--|

| MAXIMUM POWER HANDLING ( | CW)     |       |        |           |  |

| At 18 GHz                | 3 W     |       |        |           |  |

| SWITCHING TIME           |         |       |        |           |  |

|                          | < 15 ms |       |        |           |  |

| <b>RF IMPEDANCE</b>      |         |       |        |           |  |

|                          | 50 Ω    |       |        |           |  |

| FREQUENCY (GHz)          | DC – 3  | 3 – 8 | 8-12.4 | 12.4 – 18 |  |

| Isolation (dB min)       | 80      | 70    | 60     | 60        |  |

| Insertion Loss (dB max)  | 0.2     | 0.3   | 0.4    | 0.5       |  |

| VSWR                     | 1.2:1   | 1.3:1 | 1.4:1  | 1.5:1     |  |

| SM7001L SPECIFICATIONS   |               |        |         |          |           |  |

|--------------------------|---------------|--------|---------|----------|-----------|--|

| MAXIMUM POWER HANDLING ( | CW)           |        |         |          |           |  |

| At 3 GHz                 | < 100 W @ 3 G | Hz     |         |          |           |  |

| At 20 GHz                | < 40 W @ 20 G | Hz     |         |          |           |  |

| Into Termination         | < 1 W         |        |         |          |           |  |

| SWITCHING TIME           |               |        |         |          |           |  |

|                          | < 15 ms       |        |         |          |           |  |

| RF IMPEDANCE             |               |        |         |          |           |  |

|                          | 50 Ω          |        |         |          |           |  |

| FREQUENCY (GHz)          | DC – 3        | 3 – 8  | 8       | - 12.4   | 12.4 - 20 |  |

| Isolation (dB min)       | 80            | 70     | 60      |          | 60        |  |

| Insertion Loss (dB max)  | 0.2           | 0.3    | 0.4     |          | 0.5       |  |

| VSWR                     | 1.2:1         | 1.3:1  | 1.4:1   |          | 1.5:1     |  |

|                          |               |        |         |          |           |  |

| SM7002 SPECIFICATIONS    |               |        |         |          |           |  |

| MAXIMUM POWER HANDLING ( | CW)           |        |         |          |           |  |

| At 40 GHz                | 3 W           |        |         |          |           |  |

| SWITCHING TIME           |               |        |         |          |           |  |

|                          | < 15 ms       |        |         |          |           |  |

| <b>RF IMPEDANCE</b>      |               |        |         |          |           |  |

|                          | 50 Ω          |        |         |          |           |  |

| FREQUENCY (GHz)          | DC – 6        | 6 - 12 | 12 – 18 | 18 -26.5 | 26.5 -40  |  |

| Isolation (dB min)       | 70            | 60     | 60      | 55       | 50        |  |

| Insertion Loss (dB max)  | 0.2           | 0.4    | 0.5     | 0.7      | 0.9       |  |

|                          |               |        |         |          |           |  |

1.4:1

1.3:1

1.5:1

1.7:1

2.0:1

VSWR

| At 3 GHz                | < 100 W @ 3 C | GHz   |        |           |

|-------------------------|---------------|-------|--------|-----------|

| At 20 GHz               | < 40 W @ 20 C | GHz   |        |           |

| Into Termination        | < 1 W         |       |        |           |

| SWITCHING TIME          |               |       |        |           |

|                         | < 15 ms       |       |        |           |

| RF IMPEDANCE            |               |       |        |           |

|                         | 50 Ω          |       |        |           |

| FREQUENCY (GHz)         | DC – 3        | 3 – 8 | 8-12.4 | 12.4 - 20 |

| Isolation (dB min)      | 80            | 70    | 60     | 60        |

| Insertion Loss (dB max) | 0.2           | 0.3   | 0.4    | 0.5       |

| VSWR                    | 1.2:1         | 1.3:1 | 1.4:1  | 1.5:1     |

| MAXIMUM POWER HANDLING ( | CW)           |       |          |           |  |

|--------------------------|---------------|-------|----------|-----------|--|

| At 3 GHz                 | < 100 W @ 3 C | GHz   |          |           |  |

| At 20 GHz                | < 40 W @ 20 C | GHz   |          |           |  |

| Into Termination         | < 1 W         |       |          |           |  |

| SWITCHING TIME           |               |       |          |           |  |

|                          | < 15 ms       |       |          |           |  |

| RF IMPEDANCE             |               |       |          |           |  |

|                          | 50 Ω          |       |          |           |  |

| FREQUENCY (GHz)          | DC – 3        | 3 – 8 | 8 – 12.4 | 12.4 - 20 |  |

| Isolation (dB min)       | 80            | 70    | 60       | 60        |  |

| Insertion Loss (dB max)  | 0.2           | 0.3   | 0.4      | 0.5       |  |

| VSWR                     | 1.2:1         | 1.3:1 | 1.4:1    | 1.5:1     |  |

| SM7016L SPECIFICATIONS   |               |       |          |           |  |  |

|--------------------------|---------------|-------|----------|-----------|--|--|

| MAXIMUM POWER HANDLING ( | CW)           |       |          |           |  |  |

| At 3 GHz                 | < 100 W @ 3 0 | GHz   |          |           |  |  |

| At 20 GHz                | < 40 W @ 20 0 | GHz   |          |           |  |  |

| Into Termination         | < 1 W         |       |          |           |  |  |

| SWITCHING TIME           |               |       |          |           |  |  |

|                          | < 15 ms       |       |          |           |  |  |

| RF IMPEDANCE             |               |       |          |           |  |  |

|                          | 50 Ω          |       |          |           |  |  |

| FREQUENCY (GHz)          | DC – 3        | 3 – 8 | 8 – 12.4 | 12.4 - 20 |  |  |

| Isolation (dB min)       | 80            | 70    | 60       | 60        |  |  |

| Insertion Loss (dB max)  | 0.2           | 0.3   | 0.4      | 0.5       |  |  |

| VSWR                     | 1.2:1         | 1.3:1 | 1.4:1    | 1.5:1     |  |  |

## **SECTION 2**

## **PREPARATION FOR USE**

#### **INTRODUCTION**

When the SMIP *II* is unpacked from its shipping carton, the contents should include the following items:

- (1) SM7000 Series Microwave Switch module

- (1) SM7000 Series Microwave Switch User's Manual (this manual)

All components should be immediately inspected for damage upon receipt of the unit.

Once the SMIP *II* is assessed to be in good condition, it may be installed into an appropriate C-size or D-size VXIbus chassis in any slot other than slot zero. The chassis should be checked to ensure that it is capable of providing adequate power and cooling for the SMIP *II*. Once the chassis is found adequate, the SMIP *II*'s logical address and the chassis' backplane jumpers should be configured prior to the SMIP *II*'s installation.

#### **CALCULATING SYSTEM POWER AND COOLING REQUIREMENTS**

It is imperative that the chassis provide adequate power and cooling for this module. Referring to the chassis operation manual, confirm that the power budget for the system (the chassis and all modules installed therein) is not exceeded and that the cooling system can provide adequate airflow at the specified backpressure.

It should be noted that if the chassis cannot provide adequate power to the module, the instrument may not perform to specification or possibly not operate at all. In addition, if adequate cooling is not provided, the reliability of the instrument will be jeopardized and permanent damage may occur. Damage found to have occurred due to inadequate cooling would also void the warranty of the module.

#### SETTING THE CHASSIS BACKPLANE JUMPERS

Please refer to the chassis operation manual for further details on setting the backplane jumpers.

#### SETTING THE LOGICAL ADDRESS

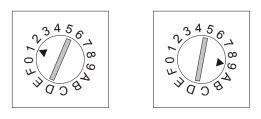

The logical address of the SMIP *II* is set by two rotary switches located on the top edge of the interface card, near the backplane connectors. Each switch is labeled with positions 0 through F. The switch closer to the front panel of the module is the least significant bit (**LSB** or "**Front**"), and the switch located towards the back of the module is the most significant bit (**MSB** or "**Back**"). To set the Logical Address (LA), simply rotate the pointer to the desired value. For example, to set the **LA** to **25**, first convert the decimal number to the hexadecimal value of **19**. Next, set the back switch to **1**, and the front switch to **9**. See Figure 2-1. Two examples are provided below:

#### **Example 1**

| LA<br>(decimal) | Divide<br>by 16 |   | MSB  | LSB            |                                                                             |

|-----------------|-----------------|---|------|----------------|-----------------------------------------------------------------------------|

| 25              | 25 / 16         | = | 1    | w/ 9 remaining | Divide the decimal value by 16 to get the MSB and the LSB.                  |

|                 |                 | = | 0001 | 1001           | The 1 is the MSB, and the remainder of 9 is the LSB.                        |

|                 |                 | = | 1    | 9              | Convert to hexadecimal. Set the back switch to 1 and the front switch to 9. |

|                 |                 |   |      | S. /           |                                                                             |

BACK

FRONT

FIGURE 2-1 LOGICAL ADDRESS EXAMPLE 1

#### Example 2

| LA<br>(decimal) | Divide<br>by 16 |   | MSB              | LSB            |                                                                             |

|-----------------|-----------------|---|------------------|----------------|-----------------------------------------------------------------------------|

| 200             | 200 / 16        | = | 12               | w/ 8 remaining | Divide by 16.                                                               |

|                 |                 | = | 1100             | 1000           | Convert to MSB and LSB.                                                     |

|                 |                 | = | С                | 8              | Convert to hexadecimal. Set the back switch to C and the front switch to 8. |

|                 |                 |   | BAC              | K              | FRONT                                                                       |

|                 |                 |   | 2 <sup>345</sup> | 61894<br>1894  |                                                                             |

FIGURE 2-2 LOGICAL ADDRESS EXAMPLE 2

Here is another way of looking at the conversion:

LA = (back switch x 16) + front switch LA = (1 x 16) + 9LA = 16 + 9LA = 25

Set the address switches to **FF** for dynamic configuration. Upon power-up, the resource manager will assign a logical address. See Section F - Dynamic Configuration in the *VXIbus Specification* for further information.

There is only one logical address per SMIP *II* base unit. Address assignments for individual modules are handled through the A24/A32 address space allocation.

#### SELECTING THE EXTENDED MEMORY SPACE

The Extended Memory Space of the SMIP *II* base units are set by a DIP-switch that is located on the bottom edge of the interface card. Position 1, located to the left on the DIP-switch, selects between A24 and A32 memory address space. In the UP position, the SMIP *II* will request A24 space. In the DOWN position (factory default), the SMIP *II* will request A32 space. (Position 2 is not currently used.) The selection of the address space should be based upon the memory allocation requirements of the system that the SMIP *II* module will be installed. The amount of memory allocated to an SMIP *II* module is independent of the address space selected.

## **SECTION 3**

### PROGRAMMING

#### **REGISTER ACCESS**

The SM7000 series modules are VXIbus register-based devices for high-speed data retrieval. Register-based programming is a series of **reads** and **writes** directly to the switch module registers. This eliminates the time for command parsing thus increasing speed.

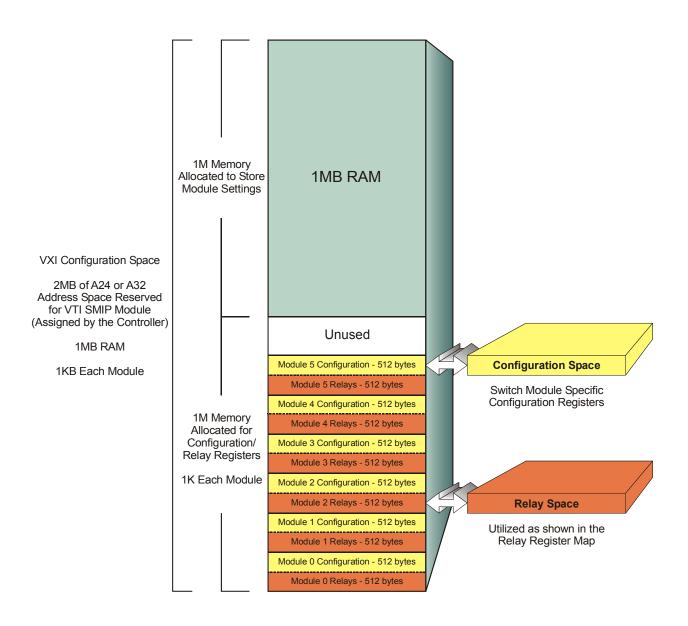

#### ADDRESSING

The VTI switching modules utilize either the A24 or A32 space of the shared-memory architecture. To read or write to a module register, a register address needs to be specified. This is done by using the offset value (assigned by the resource manager) and multiplying it by 256 or 64 k to get the base address in A24 or A32 address space, respectively

A24 Base Address = Offset value \* 0x00FF (or 256)

A32 Base Address = Offset value \* 0xFFFF (or 65,535)

The A24 or A32 offset value, assigned by the resource manager, can also be accessed by reading the A16 Offset Register. To address the A16 Offset Register use the following formula:

A16 Base Address = (Logical Address \* 64) + 0xC000 (or 49,152)

then

A16 Offset Register Address = A16 Base Address + 6

See Table 4.1 for the A16 Memory Map and the A24/A32 address space allocation.

| OFFSET | WRITE FUNCTION           | <b>READ FUNCTION</b>   |  |

|--------|--------------------------|------------------------|--|

| 0x3E   | Trace Advance            | Board Busy             |  |

| 0x3C   | Busy Trigger Control     | Busy Trigger Control   |  |

| 0x3A   | Trace RAM Control        | Trace RAM Control      |  |

| 0x38   | TTL Trigger Polarity     | Reserved               |  |

| 0x36   | Open Trigger Select      | Reserved               |  |

| 0x34   | Trace ADV Trigger Select | Reserved               |  |

| 0x32   | Trace RAM Address LOW    | Trace RAM Address LOW  |  |

| 0x30   | Trace RAM Address HIGH   | Trace RAM Address HIGH |  |

| 0x2E   | Trace RAM End LOW        | Trace RAM End LOW      |  |

| 0x2C   | Trace RAM End HIGH       | Trace RAM End HIGH     |  |

| 0x2A   | Trace RAM Start LOW      | Trace RAM Start LOW    |  |

| 0x28   | Trace RAM Start HIGH     | Trace RAM Start HIGH   |  |

| 0x26   | Module 5, 4 Used Address | Reserved               |  |

| 0x24   | Module 3, 2 Used Address | Reserved               |  |

| 0x22   | Module 1, 0 Used Address | Reserved               |  |

| 0x20   | NVM Access Register      | NVM Access Register    |  |

| 0x1E   | Reserved                 | Subclass Register      |  |

| 0x1C   | Interrupt Control        | Interrupt Control      |  |

| 0x1A   | Reserved                 | Interrupt Status       |  |

| 0x18   | Reserved                 | Reserved               |  |

| 0x16   | Reserved                 | Reserved               |  |

| 0x14   | Reserved                 | Reserved               |  |

| 0x12   | Reserved                 | Reserved               |  |

| 0x10   | Reserved                 | Reserved               |  |

| 0x0E   | Reserved                 | Version Number         |  |

| 0x0C   | Reserved                 | Serial Number LOW      |  |

| 0x0A   | Reserved                 | Serial Number HIGH     |  |

| 0x08   | Reserved                 | Reserved               |  |

| 0x06   | Offset Register          | Offset Register        |  |

| 0x04   | Control Register         | Status Register        |  |

| 0x02   | Reserved                 | Device Type Register   |  |

| 0x00   | LA Register              | ID Register            |  |

#### TABLE 4-1 SMIP II REGISTER MAP - A16

**NOTE**: As members of the SMIP *II* series, the *SM7000 Series* microwave modules allocate for six (6) module boards, but only implement Module 0. Modules 1 - 5 are unused.

#### **DESCRIPTION OF REGISTERS - A16**

The following describes the registers shown in the SMIP II Register Map for A16 address space.

#### ID Register - Read only

| ID Register (0x00) — Read Only |                   |                                                        |  |  |  |

|--------------------------------|-------------------|--------------------------------------------------------|--|--|--|

| D11-D0                         | Manufacturer's ID | VXI Technology, Inc., set to F4B <sub>16</sub>         |  |  |  |

| D13-D12                        | Address Space     | $A16/A24 = 00_2$<br>$A16/A32 = 01_2$                   |  |  |  |

| D15-D14                        | Device Class      | Extended register based device, set to 01 <sub>2</sub> |  |  |  |

| Logical Address Register (0x00) — Write Only |                 |                                                                                                                                                                                                                                                              |  |  |

|----------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| D7-D0                                        | Logical Address | Sets the new logical address in a dynamically<br>configured module. When set for dynamic<br>configuration (set to $FF_{16}$ ) a soft reset will not alter<br>the configured logical address, while a hard reset<br>will set the register back to $FF_{16}$ . |  |  |

| D15-D8                                       | Reserved        | Writing to this range has no effect.                                                                                                                                                                                                                         |  |  |

|         | Device Type Register (0x02) — Read Only |                                                                                          |  |  |  |

|---------|-----------------------------------------|------------------------------------------------------------------------------------------|--|--|--|

| D11-D0  | Model Code                              | Model 277, set to 115 <sub>16</sub>                                                      |  |  |  |

| D15-D12 | Required Memory                         | 2 Mbytes, set to 2 <sub>16</sub> , for A24<br>2 Mbytes, set to A <sub>16</sub> , for A32 |  |  |  |

|        | Status Register (0x04) — Read Only |                                                                                                                                                                   |  |  |  |  |

|--------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| D15    | A24/A32 Active                     | <ul> <li>1 = indicates that A24/A32 memory space access is<br/>enabled</li> <li>0 = indicates that A24/A32 memory space access is<br/>locked out</li> </ul>       |  |  |  |  |

| D14    | MODID*                             | <ul> <li>1 = indicates that the module is not selected by the<br/>MODID line</li> <li>0 = indicates that the module is selected by the<br/>MODID line.</li> </ul> |  |  |  |  |

| D13-D4 | Reserved                           | These bits always read as 11,1111,1111 <sub>2</sub>                                                                                                               |  |  |  |  |

| D3     | Ready                              | This bit always reads as $1_2$                                                                                                                                    |  |  |  |  |

| D2     | Passed                             | This bit always reads as $1_2$                                                                                                                                    |  |  |  |  |

| D1-D0  | Reserved                           | These bits always read as $11_2$                                                                                                                                  |  |  |  |  |

|        | Control Register (0x04) — Write Only |                                                                                                                                        |  |  |  |  |

|--------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| D15    | A24/A32 Enable                       | 1 = write a 1 to this bit to enable A24/A32 memory<br>access<br>0 = to disable access                                                  |  |  |  |  |

| D14-D2 | Reserved                             | Writes to these bits have no effect.                                                                                                   |  |  |  |  |

| D1     | Sysfail Inhibit                      | Write a 1 to this bit to prevent the module from asserting the SYSFAIL* line.                                                          |  |  |  |  |

| D0     | Reset                                | <ul> <li>1 = write a 1 to this bit to force the module into a reset state</li> <li>0 = write a 0 to release the reset state</li> </ul> |  |  |  |  |

| Offset Register (0x06) — Read and Write |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|-----------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| D15-D0                                  | A24/A32 Memory<br>Offset | The value written to this 16-bit register, times 256, sets the base address of the A24 memory space used by the module. The value written to this 16-bit register, times 65,536, sets the base address of the A32 memory space used by the module. A read from this register reflects the previously written value. Because of the required memory size, bits D4 - D0 are disregarded on writes and always read back as 0. Upon receiving a hard reset, all bits in this register are set to 0. A soft reset does not affect the value in this register. |  |  |  |

| Reserved Register (0x0A) — Read Only |                 |                                        |  |  |

|--------------------------------------|-----------------|----------------------------------------|--|--|

| D15-D0                               | Not Implemented | Always read back as FFFF <sub>16</sub> |  |  |

| Reserved Register (0x0C) — Read Only |                 |                                        |  |  |

|--------------------------------------|-----------------|----------------------------------------|--|--|

| D15-D0                               | Not Implemented | Always read back as FFFF <sub>16</sub> |  |  |

| Version Number Register (0x0E) — Read Only |                            |                                                  |  |

|--------------------------------------------|----------------------------|--------------------------------------------------|--|

| D15-D8                                     | Firmware Version<br>Number | Not applicable, reads back as $FF_{16}$          |  |

| D7-D4                                      | Major Hardware Version     | Depends on the specific hardware revision of the |  |

|                                            | Number                     | SMIP <i>II</i> interface board.                  |  |

| D3-D0                                      | Minor Hardware Version     | Depends on the specific hardware revision of the |  |

|                                            | Number                     | SMIP II interface board.                         |  |

| Interrupt Status Register (0x1A) — Read Only                                                                                                                                                                                                                                      |                                |                                                                                                                                                                                                                                                              |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| D15                                                                                                                                                                                                                                                                               | Scan Function done             | The latest scan list update is complete.                                                                                                                                                                                                                     |  |

| D14                                                                                                                                                                                                                                                                               | Openbus Active Event<br>true   | The Openbus was activated by one or more<br>programmed inputs. See description of the<br>Openbus in the module register section.                                                                                                                             |  |

| D13-D8                                                                                                                                                                                                                                                                            | Modules 0 - 5 Busy<br>complete | <ul> <li>D13 = Module 5, D12 = Module 4, and D8 = Module 0.</li> <li>The programmed Busy signal from one of the modules has timed out. This indicates that the relays actuated for that Busy cycle have settled and a measurement may take place.</li> </ul> |  |

| D7-D0                                                                                                                                                                                                                                                                             | Reserved                       | Always reads back as FFFF <sub>16</sub>                                                                                                                                                                                                                      |  |

| <b>Note</b> : This status register may be used in a polled fashion rather than allowing the events above to generate an Interrupt. A read of this register will clear any active bits. Bits that are not set, or are about to be set are not affected by a read of this register. |                                |                                                                                                                                                                                                                                                              |  |

| D7     IR ENA*     0 = writing a 0 to this bit enables interrupter capabilities       1 = writing a 1 to this bit disables interrupter capabilities                                                                                                                                                                                                                                                                                                                                  | Interrupt Control Register (0x1C) — Read and Write |                      |                                                          |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------|----------------------------------------------------------|--|

| D14       Openbus Active Event<br>true mask bit       0 = enabled<br>1 = disabled         D13-D8       Module 0 - 5 Busy<br>complete       0 = enabled<br>1 = disabled         D13-D8       Module 0 - 5 Busy<br>complete       013 = Module 5, D12 = Module 4, and D8 =<br>Module 0.         D7       IR ENA*       0 = writing a 0 to this bit enables interrupter<br>capabilities         D7       IR ENA*       0 = writing a 1 to this bit disables interrupter<br>capabilities | D15                                                |                      |                                                          |  |

| D14       true mask bit       1 = disabled         D13-D8       Module 0 - 5 Busy complete       0 = enabled         D13-D8       Module 0 - 5 Busy complete       D13 = Module 5, D12 = Module 4, and D8 = Module 0.         D7       IR ENA*       0 = writing a 0 to this bit enables interrupter capabilities         1       = writing a 1 to this bit disables interrupter capabilities                                                                                        |                                                    |                      |                                                          |  |

| D13-D8       Module 0 - 5 Busy complete       0 = enabled 1 = disabled         D13 - D8       Module 0 - 5 Busy complete       D13 = Module 5, D12 = Module 4, and D8 = Module 0.         D7       IR ENA*       0 = writing a 0 to this bit enables interrupter capabilities 1 = writing a 1 to this bit disables interrupter capabilities                                                                                                                                          | D14                                                | 1                    |                                                          |  |

| D13-D8       Module 0 - 5 Busy complete       1 = disabled         D13 = Module 5, D12 = Module 4, and D8 = Module 0.         D7       IR ENA*         0 = writing a 0 to this bit enables interrupter capabilities         1 = disabled         D7                                                                                                                                                                                                                                  |                                                    | true mask bit        |                                                          |  |

| D13-D8     Module 0 - 5 Busy<br>complete     D13 = Module 5, D12 = Module 4, and D8 =<br>Module 0.       D7     IR ENA*     0 = writing a 0 to this bit enables interrupter<br>capabilities       1 = writing a 1 to this bit disables interrupter<br>capabilities                                                                                                                                                                                                                   |                                                    |                      |                                                          |  |

| D13-D8     complete       D13 = Module 5, D12 = Module 4, and D8 = Module 0.       D7     IR ENA*       0 = writing a 0 to this bit enables interrupter capabilities       1 = writing a 1 to this bit disables interrupter capabilities                                                                                                                                                                                                                                             |                                                    | Module 0 - 5 Busy    | 1 = disabled                                             |  |

| D7     IR ENA*       D7     IR ENA*         D7     IR ENA*         D7     IR ENA*         D7     IR ENA*         D7     IR ENA*                                                                                                                                                                                                                                                                                                                                                      | D13-D8                                             | •                    |                                                          |  |

| D7 IR ENA* $\begin{array}{c} 0 = \text{writing a 0 to this bit enables interrupter} \\ capabilities \\ 1 = \text{writing a 1 to this bit disables interrupter} \\ capabilities \end{array}$                                                                                                                                                                                                                                                                                          |                                                    | complete             | D13 = Module 5, $D12 = Module 4$ , and $D8 =$            |  |

| D7 IR ENA* capabilities<br>1 = writing a 1 to this bit disables interrupter<br>capabilities                                                                                                                                                                                                                                                                                                                                                                                          |                                                    |                      | Module 0.                                                |  |

| D/     IR ENA*     1 = writing a 1 to this bit disables interrupter capabilities                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |                      | 0 = writing a 0 to this bit enables interrupter          |  |

| l = writing a l to this bit disables interrupter<br>capabilities                                                                                                                                                                                                                                                                                                                                                                                                                     | D7                                                 | IR ENA*              | capabilities                                             |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | D7                                                 |                      | 1 = writing a 1 to this bit disables interrupter         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                    |                      | capabilities                                             |  |

| The module has no interrupt handler capability;                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                    | IH ENA*              | The module has no interrupt handler capability;          |  |

| D6 IH ENA* therefore writing a 1 or 0 has no effect. A 1 is                                                                                                                                                                                                                                                                                                                                                                                                                          | D6                                                 |                      | therefore writing a 1 or 0 has no effect. A 1 is         |  |

| always read back for this bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                    |                      | always read back for this bit.                           |  |

| The complement of the value programmed into                                                                                                                                                                                                                                                                                                                                                                                                                                          | The complement of the value programmed into        |                      |                                                          |  |

| these three bits reflects the selected IRQ line use                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                    |                      | these three bits reflects the selected IRQ line used     |  |

| D5-D3 Interrupter IRQ Line by the module. A value of 011 <sub>2</sub> would select IR                                                                                                                                                                                                                                                                                                                                                                                                | D5-D3                                              | Interrupter IRQ Line | by the module. A value of $011_2$ would select IRQ4,     |  |

| a value of $000_2$ would select IRQ7, and a value of                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                    |                      | a value of $000_2$ would select IRQ7, and a value of     |  |

| $111_2$ would disconnect the IRQ lines.                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                    |                      | $111_2$ would disconnect the IRQ lines.                  |  |

| The module has no interrupt handler capability;                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                    |                      |                                                          |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | D2-D0                                              | Handler IRQ Line     | therefore writing to these bits has no effect. A $111_2$ |  |

| is always read back for these bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                    |                      |                                                          |  |

| Note that all bits in this register are set to 1 upon receipt of a hard or soft reset.                                                                                                                                                                                                                                                                                                                                                                                               |                                                    |                      |                                                          |  |

| Subclass Register (0x1E) — Read Only |                           |                             |  |

|--------------------------------------|---------------------------|-----------------------------|--|

| D15                                  | VXIbus Extended<br>Device | Always reads as 1.          |  |

| D14-D0                               | Extended Memory<br>Device | Always reads as $7FFD_{16}$ |  |

| NVM Access Resister (0x20) — Read Only |        |                                                                                                                                                  |

|----------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| D15-D1                                 | Unused | All Bits are always 1.                                                                                                                           |

| D0                                     |        | Reads back the serial data stream from the selected SMIP <i>II</i> board.<br>Note that only one SMIP <i>II</i> board may be read back at a time. |

| NVM Access Resister (0x20) — Write Only |        |                                                                     |

|-----------------------------------------|--------|---------------------------------------------------------------------|

| D15-D7                                  | Unused | Data written to these bits have no effect.                          |

| D6                                      |        | Serial clock for module 5; should be a logic 1 when not used.       |

| D5                                      |        | Serial clock for module 4; should be a logic 1 when not used.       |

| D4                                      |        | Serial clock for module 3; should be a logic 1 when not used.       |

| D3                                      |        | Serial clock for module 2; should be a logic 1 when not used.       |

| D2                                      |        | Serial clock for module 1; should be a logic 1 when not used.       |

| D1                                      |        | Serial clock for module 0; should be a logic 1 when not used.       |

| D0                                      |        | Serial data input for all modules; must be a logic 1 when not used. |

| Board X, Y Used Address Register (0x22, 0x24, 0x26) — Read and Write |                                                                                      |  |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|

| D15-D8                                                               | Sets the actual number of words of address space used by the relays on board's X.    |  |

| D7-D0                                                                | Sets the actual number of words of address space used by the relays<br>on board's Y. |  |

| Trace RAM Start High Register (0x28) — Read and Write |        |                                                                                                                                              |

|-------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------|

| D15-D4                                                | Unused | Data written to these bits have no effect and always read back as 1.                                                                         |

| D3-D0                                                 |        | Sets the four most significant bits of the starting address of the Trace RAM, allowing the available RAM to be divided into multiple traces. |

| Trace RAM Start Low Register (0x2A) — Read and Write |                                                                                                                                             |  |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| D15-D0                                               | Sets the 16 least significant bits of the starting address of the Trace RAM, allowing the available RAM to be divided into multiple traces. |  |

| Trace RAM End High Register (0x2C) — Read and Write |        |                                                                                                                                            |

|-----------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------|

| D15-D4                                              | Unused | Data written to these bits have no effect and always read back as 1.                                                                       |

| D3-D0                                               |        | Sets the four most significant bits of the ending address of the Trace RAM, allowing the available RAM to be divided into multiple traces. |

| Trace RAM End Low Register (0x2E) — Read and Write |                                                                                                                                           |  |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| D15-D0                                             | Sets the 16 least significant bits of the ending address of the Trace RAM, allowing the available RAM to be divided into multiple traces. |  |

| Trace RAM Address HIGH Register (0x30) — Read and Write |        |                                                                                                                                                                     |

|---------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D15-D4                                                  | Unused | Data written to these bits have no effect and always read back as 1.                                                                                                |

| D3-D0                                                   |        | Sets and reads back the four most significant bits of the current<br>address of the Trace RAM, allowing the current trace RAM address<br>to be queried and changed. |

| Trace RAM Address LOW Register (0x32) — Read and Write |                                                                                                                                                                         |  |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| D15-D0                                                 | Sets and reads back the sixteen least significant bits of the current<br>address of the Trace RAM, allowing the current trace RAM address<br>to be queried and changed. |  |

| Trace Advance Trigger Select Register (0x34) —Write Only |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |